Correspondência:info@anke-pcb.com

WhatApp/WeChat: 008618589033832

Skype: SannyduAnBsp

Três aspectos para garantir a integridade de energia emDesign de PCB

No design eletrônico moderno, a integridade de energia é uma parte indispensável do design da PCB. Para garantir a operação e o desempenho estáveis dos dispositivos eletrônicos, devemos considerar e projetar de forma abrangente da fonte de energia ao receptor.

Ao projetar e otimizar cuidadosamente os módulos de energia, aviões de camada interna e chips de fonte de alimentação, podemos realmente alcançar a integridade de energia. Este artigo se aprofundará nesses três aspectos principais para fornecer orientação e estratégias práticas para os designers de PCB.

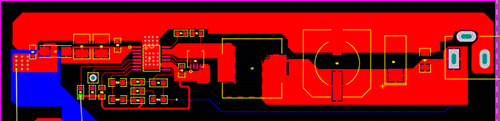

I. Fiação do layout do módulo de energia

O módulo de energia é a fonte de energia de todos os dispositivos eletrônicos, seu desempenho e layout afetam diretamente a estabilidade e a eficiência de todo o sistema. O layout e o roteamento corretos podem não apenas reduzir a interferência de ruído, mas também garantir o fluxo de corrente suave, melhorando assim o desempenho geral.

2. Layout do módulo de potência

1. Processamento da fonte:

O módulo de energia deve receber atenção especial, pois serve como ponto de partida do poder. Para reduzir a introdução do ruído, o ambiente ao redor do módulo de energia deve ser mantido o mais limpo possível para evitar adjacência a outrosalta frequênciaou componentes sensíveis ao ruído.

2.Come o chip da fonte de alimentação:

O módulo de energia deve ser colocado o mais próximo possível do chip fornecido por energia. Isso pode reduzir as perdas no processo de transmissão atual e reduzir os requisitos de área do plano da camada interna.

3. Considerações de dissipação de calor:

O módulo de potência pode gerar calor durante a operação, portanto, é garantido que não haja obstruções acima dele para a dissipação de calor. Se necessário, dissipadores de calor ou ventiladores podem ser adicionados para resfriamento.

4.Aviding Loops:

Ao rotear, evite formar loops de corrente para reduzir a possibilidade de interferência eletromagnética.

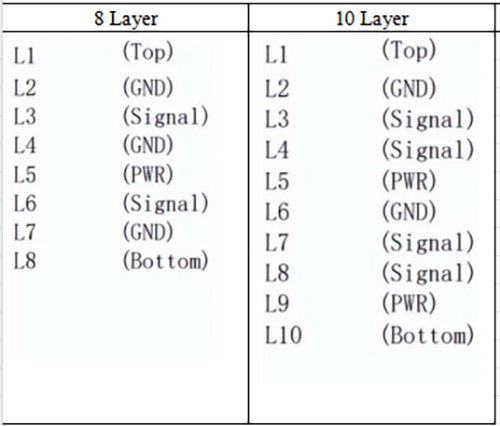

Ii. Planejamento de design de avião da camada interna

A. Design de pilha de camadas

In Design PCB EMC, o design da pilha de camadas é um elemento -chave que precisa considerar o roteamento e a distribuição de energia.

um. Para garantir as características de baixa impedância do plano de potência e absorver o acoplamento de ruído do solo, a distância entre os planos de energia e terra não deve exceder 10mil, normalmente recomendada como menor que 5mil.

b. Se um único plano de potência não puder ser implementado, uma camada de superfície poderá ser usada para estabelecer o plano de potência. Os planos de potência e terreno intimamente adjacentes formam um capacitor plano com impedância CA mínima e excelentes características de alta frequência.

c. Evite duas camadas adjacentes de potência, especialmente com grandes diferenças de tensão, para evitar o acoplamento de ruído. Se inevitável, aumente o espaçamento entre as duas camadas de potência o máximo possível.

d. Os planos de referência, especialmente os planos de referência de energia, devem manter características de baixa impedância e podem ser otimizadas através de capacitores de desvio e ajustes de camada.

B. segmentação de energia do múltiplo

um. Para fontes de energia específicas de pequena alcance, como a tensão de trabalho do núcleo de um certo chip de IC, o cobre deve ser colocado na camada de sinal para garantir a integridade do plano de potência, mas evite colocar o cobre de potência na camada de superfície para reduzir a radiação de ruído.

b. A seleção da largura da segmentação deve ser apropriada. Quando a tensão é maior que 12V, a largura pode ser de 20 a 30mil; Caso contrário, escolha 12-20mil. A largura da segmentação entre as fontes de energia analógica e digital precisa ser aumentada para impedir que a energia digital interfira na potência analógica.

c. Redes de energia simples devem ser concluídas na camada de roteamento e redes de energia mais longas devem ter os capacitores de filtro adicionados.

d. O plano de potência segmentado deve ser mantido regularmente para evitar formas irregulares, causando ressonância e aumento da impedância de energia. Tiras longas e estreitas e divisões em forma de halteres não são permitidas.

C. filtragem do plano

um. O plano de potência deve estar intimamente acoplado ao plano de terra.

b. Para chips com frequências operacionais, excedendo 500 MHz, depende principalmente da filtragem do capacitor plano e use uma combinação de filtragem de capacitores. O efeito de filtragem precisa ser confirmado por simulação de integridade de energia.

c. Instale os indutores para desacoplar os capacitores no plano de controle, como ampliar os fios do capacitor e o aumento do capacitor Vias, para garantir que a impedância do solo de energia seja menor que a impedância alvo.

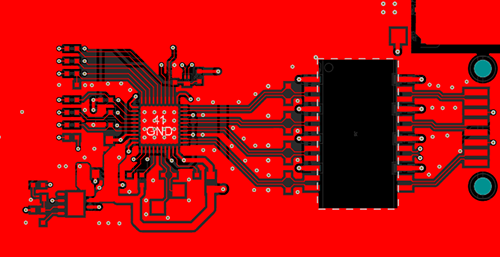

Iii. Fiação de layout do chip de energia

O chip de energia é o núcleo dos dispositivos eletrônicos e garantir que sua integridade de energia seja crucial para melhorar o desempenho e a estabilidade do dispositivo. O controle de integridade de potência para chips de energia envolve principalmente o manuseio de pinos de potência do chip e o layout correto e a fiação dos capacitores de desacoplamento. A seguir, detalhará considerações e conselhos práticos sobre esses aspectos.

A.Chip Power Pin Routing

O roteamento dos pinos de potência do chip é uma parte crucial do controle de integridade de energia. Para fornecer uma oferta de corrente estável, recomenda -se engrossar o roteamento dos pinos de energia, geralmente para a mesma largura que os pinos de chip. Normalmente, olargura mínimaNão deve ser inferior a 8mil, mas, para melhores resultados, tente obter uma largura de 10mil. Ao aumentar a largura do roteamento, a impedância pode ser reduzida, reduzindo assim o ruído de potência e garantindo uma oferta de corrente suficiente ao chip.

B. Layout e roteamento de capacitores de dissociação

Os capacitores de desacoplamento desempenham um papel significativo no controle de integridade de energia para chips de energia. Dependendo das características do capacitor e dos requisitos de aplicação, os capacitores de desacoplamento geralmente são divididos em grandes e pequenos capacitores.

um. Grandes capacitores: os grandes capacitores geralmente são distribuídos uniformemente ao redor do chip. Devido à sua menor frequência ressonante e raio de filtragem maior, eles podem efetivamente filtrar o ruído de baixa frequência e fornecer fonte de alimentação estável.

b. Pequenos capacitores: os pequenos capacitores têm uma frequência ressonante mais alta e um raio de filtragem menor, para que eles sejam colocados o mais próximo possível dos pinos do chip. Colocá-los muito longe pode não filtrar efetivamente o ruído de alta frequência, perdendo o efeito de desacoplamento. O layout correto garante que a eficácia dos pequenos capacitores na filtragem de ruído de alta frequência seja totalmente utilizada.

C. Método de fiação de capacitores de desacoplamento paralelo

Para melhorar ainda mais a integridade de energia, vários capacitores de desacoplamento são frequentemente conectados em paralelo. O principal objetivo dessa prática é reduzir a indutância equivalente em série (ESL) de capacitores individuais através da conexão paralela.

Ao paralelar vários capacitores de desacoplamento, deve -se prestar atenção à colocação de Vias para capacitores. Uma prática comum é compensar as vias do poder e do solo. O principal objetivo disso é reduzir a indutância mútua entre a desacoplamento dos capacitores. Certifique -se de que a indutância mútua seja muito menor que a ESL de um único capacitor, de modo que a impedância geral da ESL após paralelo a vários capacitores de desacoplamento seja 1/n. Ao reduzir a indutância mútua, a eficiência da filtragem pode ser efetivamente aprimorada, garantindo maior estabilidade de energia.

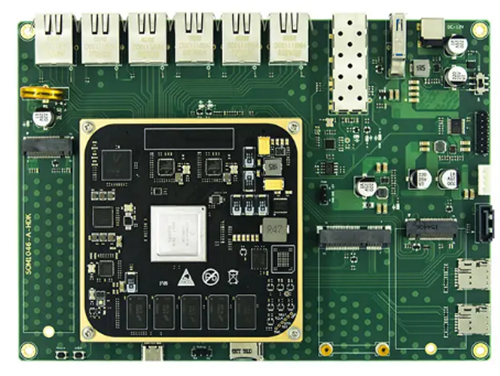

Layoute roteamento de módulos de potência, planejamento de projeto de plano da camada interna e manuseio correto do layout e fiação do chip de energia são indispensáveis no design de dispositivos eletrônicos. Através do layout e roteamento adequados, podemos garantir a estabilidade e a eficiência dos módulos de energia, reduzir a interferência de ruído e melhorar o desempenho geral. Projeto de pilha de camadas e segmentação de várias potências otimizam ainda mais as características dos planos de energia, reduzindo a interferência do ruído de energia. O manuseio adequado do layout do chip de energia e os capacitores de fiação e desacoplamento são cruciais para o controle da integridade de energia, garantindo uma oferta de corrente estável e filtragem de ruído eficaz, aprimorando o desempenho e a estabilidade do dispositivo.

No trabalho prático, vários fatores, como magnitude atual, largura de roteamento, número de vias, efeitos de acoplamento etc., precisam ser considerados de forma abrangente para tomar decisões racionais de layout e roteamento. Siga as especificações do projeto e as melhores práticas para garantir o controle e otimização da integridade de energia. Somente dessa maneira podemos fornecer uma fonte de energia estável e eficiente para dispositivos eletrônicos, atender às crescentes demandas de desempenho e impulsionar o desenvolvimento e o progresso da tecnologia eletrônica.

Shenzhen Anke PCB Co., Ltd

Hora de postagem: 25-2024 de março